问:什么是TTL电平?

答:TTL是“晶体管-晶体管逻辑”(Transistor-Transistor Logic)的缩写,是一种广泛使用的数字电路电平标准。它定义了电路中高电平(逻辑“1”)和低电平(逻辑“0”)的电压范围。在标准TTL电路中,高电平通常为2.4V至5V,低电平为0V至0.8V。这一标准由德州仪器公司于20世纪60年代提出,因其稳定性高、响应速度快,成为早期数字电路设计的核心基础。

问:TTL电平的工作原理是什么?

答:TTL电路的核心是晶体管逻辑门(如与门、或门、非门)。其工作原理基于晶体管的开关特性:

- 输入高电平(逻辑1):当输入电压≥2.0V时,晶体管导通,输出端通过内部电路被拉低至接近0V(实际输出低电平)。

- 输入低电平(逻辑0):当输入电压≤0.8V时,晶体管截止,输出端通过上拉电阻提供高电平(约3.5V-5V)。

通过这种开关机制,TTL电路能够实现逻辑运算和信号传输。

问:TTL电平的典型应用场景有哪些?

答:TTL电平主要用于以下领域:

- 数字电路设计:如逻辑门、计数器、触发器等基础电路模块。

- 微控制器接口:早期单片机(如8051)的GPIO引脚常采用TTL电平通信。

- 传感器信号传输:部分传感器输出信号兼容TTL电平(如红外接收模块)。

- 工业控制设备:PLC(可编程逻辑控制器)的I/O模块常采用TTL标准。

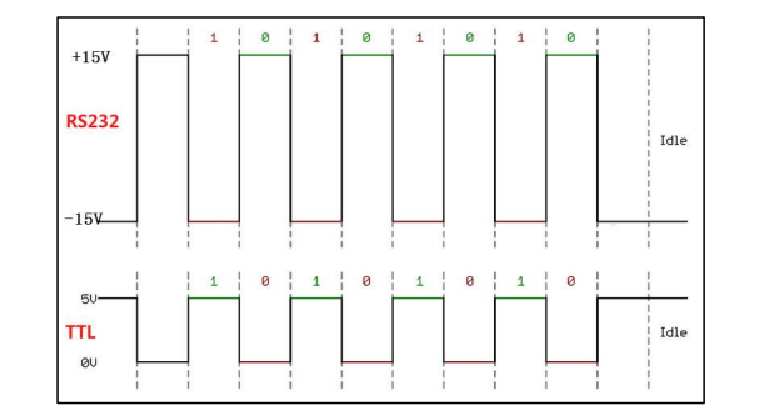

- 早期计算机系统:如IBM PC的串口(RS-232)虽使用负逻辑,但需通过电平转换芯片与TTL对接。

问:TTL电平有哪些优缺点?

答:

优点:

- 响应速度快:典型延迟仅10纳秒级,适合高频信号处理。

- 抗干扰能力强:高低电平间电压差大(约2V以上),减少误判风险。

- 驱动能力强:标准TTL门可驱动10个以上同类负载。

缺点:

- 功耗较高:晶体管导通时电流较大,导致整体功耗上升。

- 电压兼容性差:与CMOS等低压电路直接连接可能需电平转换。

- 噪声敏感:高速切换时可能因信号反射引发噪声问题。

问:TTL电平与CMOS电平有什么区别?

答:主要区别如下:

| 特性 | TTL | CMOS |

|---|---|---|

| 电源电压 | 5V(标准) | 3V-18V(宽范围) |

| 功耗 | 较高(毫瓦级) | 极低(微瓦级) |

| 抗噪能力 | 较强 | 较弱(需额外保护) |

| 电平范围 | 高电平≥2.4V,低电平≤0.8V | 高电平≈电源电压,低电平≈0V |

| 输入阻抗 | 较低(千欧级) | 极高(兆欧级) |

问:TTL电路中的“推挽输出”和“开漏输出”有何不同?

答:这是两种常见的输出结构:

- 推挽输出(Push-Pull):

- 内部包含上拉(PNP晶体管)和下拉(NPN晶体管)结构,可直接输出高电平或低电平。

- 优点:驱动能力强,信号边沿陡峭。

- 应用:多数标准TTL门电路采用此结构。

- 开漏输出(Open-Drain):

- 仅包含下拉晶体管,高电平需外接上拉电阻实现。

- 优点:支持总线“线与”功能,多设备共享信号线时不易冲突。

- 应用:I²C总线、部分中断信号设计。

问:如何解决TTL与其他电平标准(如CMOS、RS-232)的兼容问题?

答:常见解决方案包括:

- 电平转换芯片:如74LVC系列(TTL转CMOS)、MAX232(TTL转RS-232)。

- 电阻分压网络:通过串联电阻降低高压信号(如5V→3.3V)。

- 二极管钳位:限制输入电压不超过TTL承受范围。

- 光耦隔离:用于长距离传输或需电气隔离的场景。

问:TTL电路中常见的故障现象有哪些?如何排查?

答:

典型故障:

- 逻辑错误:输出电平与预期不符(如常高/常低)。

- 信号延迟:电路响应速度明显变慢。

- 发热异常:芯片或元件温度过高。

排查步骤:

- 检查电源:确认5V供电稳定(误差≤±10%)。

- 测量输入/输出电平:用万用表或示波器验证信号是否符合TTL标准。

- 替换元件:怀疑损坏的芯片或晶体管可用同型号替换测试。

- 检查负载:避免驱动超出器件能力的负载数量。

- 分析信号完整性:高频场景下需排查信号反射、串扰等问题。

问:如何测试TTL电平信号?

答:常用工具与方法:

- 万用表:测量静态电压是否在0.8V(低)或2.4V(高)以上。

- 示波器:观察信号波形,检查上升/下降时间、过冲等动态特性。

- 逻辑分析仪:捕获多路信号时序,分析逻辑关系。

- 在线测试(ICT):通过测试点验证电路节点状态。

测试时需注意接地可靠性,避免探头引入干扰。

问:设计TTL电路时需要注意哪些关键点?

答:

- 电源去耦:每个芯片电源引脚就近添加0.1μF电容,抑制高频噪声。

- 信号完整性:高频信号线尽量短,必要时串联阻尼电阻(如22Ω)。

- 负载匹配:单个门电路驱动负载不超过其扇出系数(标准TTL为10)。

- 未用引脚处理:闲置输入引脚需接高电平(通过上拉电阻)或接地,避免悬空引发振荡。

- 散热设计:大电流器件需预留散热空间。

问:TTL芯片的命名规则是什么?如何选型?

答:

命名规则:

- 系列前缀:如74(标准TTL)、74LS(低功耗肖特基)、74F(高速)。

- 功能编号:如00(四路2输入与非门)、04(六路反相器)。

- 封装后缀:如N(塑料双列直插)、D(表面贴装)。

选型建议:

- 速度需求:高速场景选74F系列,低功耗选74LS。

- 供电电压:确认芯片支持5V供电(部分新型号兼容3.3V)。

- 封装类型:根据PCB布局选择DIP或SMD封装。

- 驱动能力:高负载场景需选择大电流型号(如74HCT系列)。

TTL电平作为数字电路的经典标准,凭借其稳定性和易用性,至今仍在工业控制、嵌入式系统等领域广泛应用。理解其原理与设计要点,不仅能帮助工程师高效解决电路兼容性问题,也为深入学习现代电子技术奠定了重要基础。通过合理选型与规范设计,TTL电路仍可满足多数中低速场景下的可靠需求。

免责声明:文章内容来自互联网,本站不对其真实性负责,也不承担任何法律责任,如有侵权等情况,请与本站联系删除。

转载请注明出处:TTL电平是什么 https://www.yhzz.com.cn/a/24913.html