前言

上篇文章讲了高速串行总线中的数据包核参考时钟的相关内容,见:高速串行总线设计基础(六)揭秘SERDES高速面纱之数据包与参考时钟要求,但SERDES的秘密还没有完全揭开,高速串行总线技术环环相扣,缺一不可,本篇继续介绍!

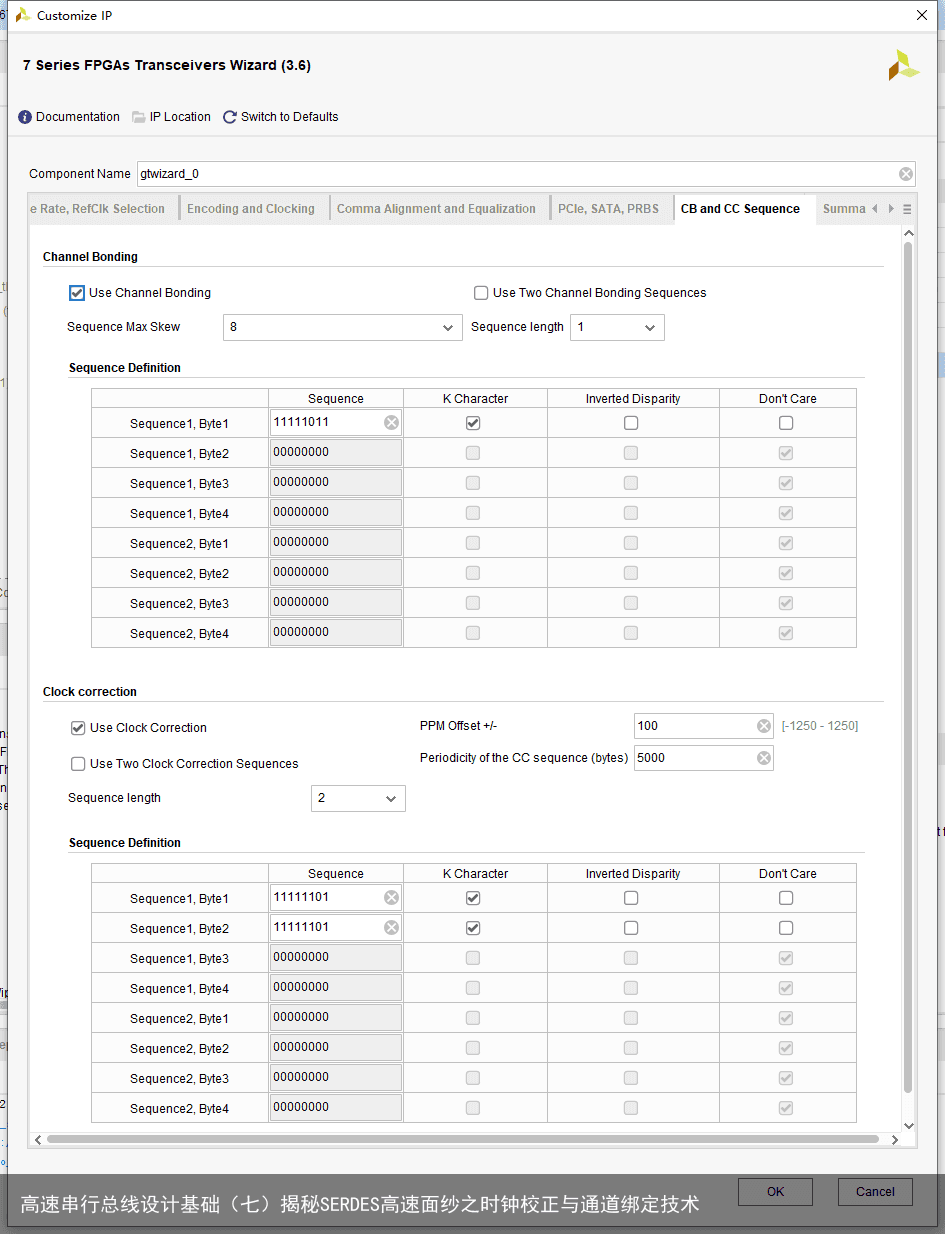

时钟校正与通道绑定技术在多通道Serdes或者Transceiver中十分常用,例如如下Xilinx Transceiver的定制选项:  尽管对于FPGA工程师只需要操作定制化的GUI选项,但是对于通道绑定以及时钟校正的了解还是很有必要的,君不知使用是建立在理解的基础之上的。

尽管对于FPGA工程师只需要操作定制化的GUI选项,但是对于通道绑定以及时钟校正的了解还是很有必要的,君不知使用是建立在理解的基础之上的。

下面从一般的情况下对二者进行介绍,后续文章会涉略具体的transceiver的技术理解。

时钟校正

时钟校正技术是高速串行总线中几乎必要的技术,例如Xilinx 7系列的Transceiver,使用了一个弹性缓冲空间即FIFO来做时钟校正:

在后续文章具体介绍吉比特收发器协议时候会特定分析,这里给出通常情况下的时钟校正技术。

在后续文章具体介绍吉比特收发器协议时候会特定分析,这里给出通常情况下的时钟校正技术。

参考时钟源之间总是有一个很小的频率差异(通常是~+/-100ppm),即使它们名义上是相同的频率。因此,在每个MGT使用自己的参考时钟的系统中,每个MGT对其传输数据路径(TX)和接收数据路径(RX)使用的频率略有不同。 许多协议通过使用时钟校正来简化时钟。在时钟校正中,每个MGT包括一个异步FIFO。RX数据使用来自CDR(Clock and Data-Recovery)的串行时钟写入FIFO,并使用来自系统其他部分的并行时钟(本地时钟)从FIFO中读取,通常与用于TX的并行时钟相同。

时钟校正概念图

时钟校正概念图

由于CDR(Clock and Data-Recovery)时钟和本地时钟并不完全相同,除非进行校正,否则FIFO最终会溢出或不足。为了允许修正,每个MGT周期性地传送一个或多个特殊字符,允许接收方根据需要在FIFO中删除或复制这些字符。通过在FIFO太满时移除字符,在FIFO太空时复制字符,接收器可以防止溢出/下溢。这些特殊字符通常被称为SKIP。

大多数SERDES都内置了时钟校正选项。时钟校正涉及到数据流中其他地方找不到的唯一符号或符号序列。 时钟校正必须经常发生,以允许丢弃或重复以补偿时钟差异。通常,时钟校正序列也将与空闲序列相同。

一些系统不需要时钟校正。例如,在许多芯片间应用中,同一振荡器将为所有发送器提供参考时钟。使用相同的参考时钟和相同的速率意味着无需时钟校正。而且,当所有接收电路均从恢复的时钟开始计时时,不需要时钟校正。如果以相同的速率清空FIFO,则无需进行时钟校正。

同样,当所有发送参考时钟都使用外部PLL锁定到公共参考时,也不需要时钟校正。下列出了时钟校正序列之间的最大时钟数及其在各种振荡器频率下的精度。

时钟校正表

时钟校正表

接收和发送缓冲区

接收和发送缓冲区或FIFO是多吉比特收发器的主要数字接口。通常在这里写入和读取数据。在发送端,通常有一个小的FIFO,它要求读和写时钟是同步的(频率匹配,但不一定相位匹配)。

这里所谓的同步,即等时:频率匹配,但不一定相位匹配;

如果tx_write和tx_read选通脉冲的频率不完全相同,则使用不同的方案。此处,使用了较大的FIFO,并不断监视其当前状态。如果FIFO被填满,它将最终溢出。在这种情况下,将监视传入流中是否有空闲符号。遇到这些空闲字符时,不会将它们写入FIFO。

相反,如果在输出上找到空闲时FIFO处于低电平,则将数据带给用户。写指针未移动,导致重复空闲。重要的是,使用空闲符号代替字节对齐,逗号符号,时钟校正序列或通道绑定序列。所有这些都是在下游以一定的保证传输速率下所需要的。

MGT中内置的接收FIFO通常比发送(Tx)缓冲区深得多。其主要目的是允许进行时钟校正和通道绑定。

什么是通道绑定呢?下面给出答案!

通道绑定

有时,需要移动的数据量超出一个串行链路所能容纳的范围。在这些情况下,并行使用多个链路来传输数据。完成此操作后,输入流必须对齐。此过程通常称为通道绑定。通道绑定吸收了两个或多个MGT之间的偏斜,并将数据呈现给用户,就好像它是通过单个链路传输的一样。

许多协议将多个MGT连接结合起来,以创建一个单一的高吞吐量通道(如XAUI、PCI Express)。除非每个串行通道的长度完全相同,否则通道之间的偏斜会导致同一时间传输的数据在不同时间到达。

如下图示:

如上图通道绑定的示意图,通道绑定应该可以说是上述众多技术中最容易理解的技术了,下面给出定义:通道绑定即吸收两个或多个MGT之间的偏斜并将数据呈现给用户,就好像它是通过单个链路传输的一样。

如上图通道绑定的示意图,通道绑定应该可以说是上述众多技术中最容易理解的技术了,下面给出定义:通道绑定即吸收两个或多个MGT之间的偏斜并将数据呈现给用户,就好像它是通过单个链路传输的一样。

通道绑定定义中提到了多个MGT之间的数据偏斜,通俗点说就是数据之间不对齐,如果在同一时刻采样数据,可能采样不到正确的对齐数据,导致这种偏斜的因素可能有哪些呢?

造成多个MGT之间数据偏斜的原因有如下几个:

传输路径长度的差异传输路径上的有源中继器因时钟校正而产生的差异锁定/字节对齐的时间差异总之,在多个高速串行通道中,由于环境的差异,会带来数据偏斜的问题,这很容易想象,虽说条条大路通罗马,但通往罗马的途中,不同道路遇到的阻碍是不同的,到达终点的时刻也是不同的。

既然如此,通道绑定技术是如何做到好像不感知数据偏斜而正确接收数据的呢?

通道绑定允许MGT补偿多个通道之间的偏移。MGT都会同时传输一个通道绑定字符(或字符序列)。当接收到该序列时,接收的MGT可以确定它们之间的偏移,然后调整其接收数据通路中的FIFO的延迟来进行补偿。

通道绑定序列必须唯一且可扩展,并且在下游必须忽略,因为它可能会添加或删除。通常,时钟校正序列和通道绑定序列之间的符号数最少。许多基于8b / 10b的标准协议在时钟校正和通道绑定序列之间指定了至少四个符号。因此,四个符号或字节是公共的分隔距离。

参考文献

ug476_7Series_Transceivers

Multi-gigabit transceiver

高速串行总线设计基础(六)揭秘SERDES高速面纱之数据包与参考时钟要求

GTX-Channel-Bonding-in-kintex-7

pg168-gtwizard

免责声明:文章内容来自互联网,本站不对其真实性负责,也不承担任何法律责任,如有侵权等情况,请与本站联系删除。

转载请注明出处:高速串行总线设计基础(七)揭秘SERDES高速面纱之时钟校正与通道绑定技术 https://www.yhzz.com.cn/a/13502.html