前言

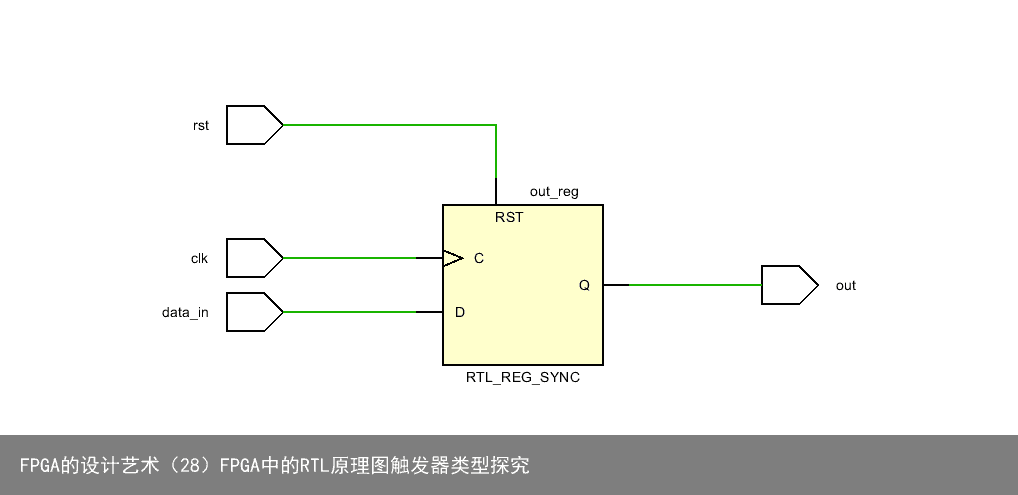

我曾经有一个疑问,就是为什么我明明使用了同步复位的设计,而Vivado给我生成的RTL原理图看似异步的? 例如:

module syn_rst( input rst, input clk, input data_in, output out ); reg out; always@(posedge clk) begin if(rst) out <= 1b0; else out <= data_in; end endmodule这看上去就是一个触发器,RST是触发器的复位引脚? 可是我的逻辑设计的是一个同步复位的逻辑,为什么会这样呢? 你是否也有同样的疑问? 我原本期待的RTL原理图类似于:

通过一个多路选择器,rst生效也需要在时钟的上升沿进行。

为此,我还在CSDN的论坛上问道过这个问题:用Verilog 设计的同步复位,综合出来的结果却是异步复位的?

当然,论坛还是不靠谱的,xia ji儿回答的居多。 不过,有一个回答是正确的,看了这篇文章,你一定知道哪一个回答是正确的了。

Vivado中的触发器

给一个提示,就是这个原理图:

这就是问题所在!

看这个寄存器的名字:RTL_REG_SYNC,SYNC是什么?是同步的含义,所以,我们有必要探究一下,Xilinx 的FPGA中的触发器?

根据Xilinx的手册WP275: 可以得知,Xilinx的触发器有支持异步复位和置位控制的,也有支持同步复位与置位控制的。 上述的例子就是具有同步复位端的触发器,它的特点是复位端口名称为:RST,置位端口名称为:SET,如下图:

而异步复位端口名称为:CLR,置位端口名称为:PRE。

且显著的特征为触发器的名称为:RTL_REG_ASYNC。

我们可以穷尽一个触发器的资源利用,例如可以同时使用同步复位,同步置位操作,也可以同时使用异步复位以及异步置位操作,但是不存在一个触发器有同步以及异步两种混合功能的情况,这是资源的特征决定的。

为了验证上述情况,我们假设一个例子,以2分频的分频器为例,讨论4种组合的情况,来看资源是如何使用的:

同步复位,同步置位

RTL描述:

always@(posedge clk) begin if(rst) begin div_clk <= 1b0; end else if(set) begin div_clk <= 1b1; end else begin div_clk <= ~div_clk; end endRTL原理图:

可见,一个同步触发器搞定。

异步复位,异步置位

RTL描述:

always@(posedge clk or posedge rst or posedge set) begin if(rst) begin div_clk <= 1b0; end else if(set) begin div_clk <= 1b1; end else begin div_clk <= ~div_clk; end end可见,一个异步触发器搞定!

异步复位,同步置位

RTL描述:

always@(posedge clk or posedge rst) begin if(rst) begin div_clk <= 1b0; end else if(set) begin div_clk <= 1b1; end else begin div_clk <= ~div_clk; end end可见,异步复位,同步置位操作,使用了一个异步触发器,但是置位并没有使用异步置位端,而是通过选择器间接实现了一个同步置位的选择。符合我们的预期。

同步复位,异步置位

RTL描述:

always@(posedge clk or posedge set) begin if(rst) begin div_clk <= 1b0; end else if(set) begin div_clk <= 1b1; end else begin div_clk <= ~div_clk; end end可见,使用了一个同步复位的触发器,且同步置位端也没有使用,而是通过一个选择器来实现,但是这种实现的方式,貌似也没有实现异步置位的操作!

我们可以通过仿真来看验证下,我们的设计是上升沿作为时钟的有效沿,仿真的时候我们在时钟的下降沿给一个置位信号,观察是否立即置位了? 如果立即置位了,则表明符合预期,否则不符合我们的设计:  可见,也实现了异步置位的行为。

可见,也实现了异步置位的行为。

可见,这个RTL原理图生成的并不完美,且让人疑惑,或者什么原因,谁来解释一下也行,欢迎!

这篇文章到此也算告一段落,我们也留有些许遗憾,但没关系,总会解决的。

我们也为下一篇博文做一下考虑,就是上述讨论都只是针对RTL层面,可知对于FPGA的开发,FPGA内部实际的资源和RTL原理图中的资源并不一样,例子RTL原理图中可以使用MUX,但是FPGA内部是用LUT代替MUX的,因此,对于综合这一步的逻辑行为是什么样子的呢? 针对最后一种情况,我们可以提前给出综合后的原理图:

可见,对于MUX以及反向器的替代,使用了一个3输入的LUT。内部的触发器也没有了同步复位端,rst以及set都作为了LUT输入的一部分。

可见,对于MUX以及反向器的替代,使用了一个3输入的LUT。内部的触发器也没有了同步复位端,rst以及set都作为了LUT输入的一部分。

LUT是FPGA的一大特色,可以看做存储3输入的所有组合,因此和一个ROM很类似,配合触发器,就可以很强大,更多内容我们下一篇再见。

最后强调一句,这些东西在Xilinx家的数据手册上都有,例如RTL原理图中可以使用的所有器件,都在数据手册中,其实就是一个库,实现一个电路,要从库中挑选器件实现它。

可参考:

https://www.xilinx.com/support/documentation/sw_manuals/xilinx14_2/7series_hdl.pdf

免责声明:文章内容来自互联网,本站不对其真实性负责,也不承担任何法律责任,如有侵权等情况,请与本站联系删除。

转载请注明出处:FPGA的设计艺术(28)FPGA中的RTL原理图触发器类型探究 https://www.yhzz.com.cn/a/12352.html