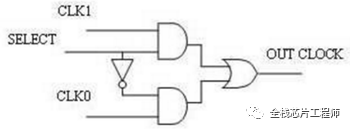

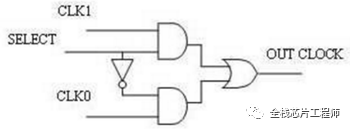

芯片运行过程中需要时钟切换时,要考虑到是否会产生glitch,小小的glitch有可能导致电路运行的错误。所以时钟切换时需要特别的处理。直接使用MUX进行时钟切换或者采用如下电路结构进行时钟切换:assign outclock = select? clk1: clk0;assignoutclock = (clk1 & select) | (~select & clk0); 两种做法都会产生时钟切换毛刺的,芯片系统很容易进入亚稳态的情况。

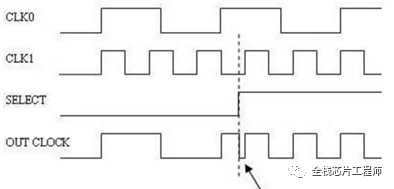

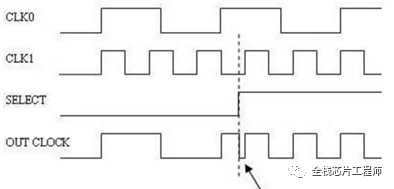

两种做法都会产生时钟切换毛刺的,芯片系统很容易进入亚稳态的情况。 为了解决时钟切换的毛刺问题,对于时钟源分为同步和异步的情况,分为如下两种解决方案:CLK0与CLK1为同步时钟源,即CLK0与CLK1成整数倍关系:插入下降沿触发的D触发器,当前已打开的时钟路径上的时钟会在其下降沿之后先关闭,然后待打开时钟路径上的时钟在其下降沿之后即打开。如下所示:从下图第二个箭头开始,实际发生时钟切换。

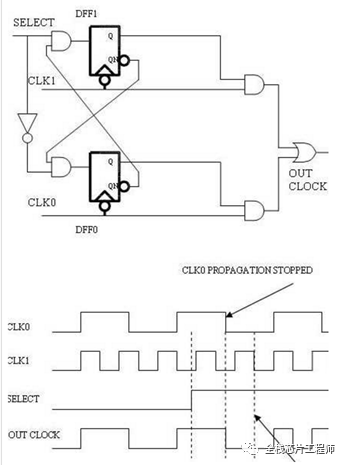

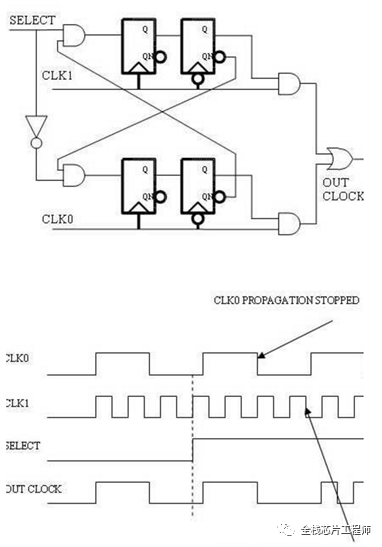

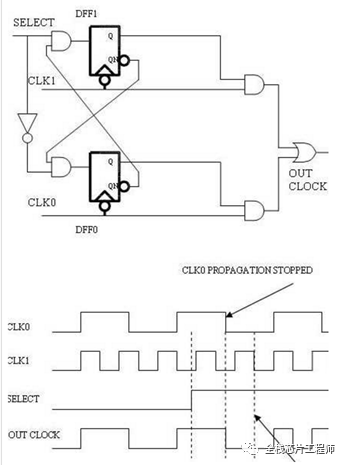

为了解决时钟切换的毛刺问题,对于时钟源分为同步和异步的情况,分为如下两种解决方案:CLK0与CLK1为同步时钟源,即CLK0与CLK1成整数倍关系:插入下降沿触发的D触发器,当前已打开的时钟路径上的时钟会在其下降沿之后先关闭,然后待打开时钟路径上的时钟在其下降沿之后即打开。如下所示:从下图第二个箭头开始,实际发生时钟切换。 CLK0与CLK1为无关时钟源,即异步时钟源在第一种方法的基础上,在选择路径上再插入一个上升沿触发D触发器,这是对异步信号进行同步处理,这样即使是两个异步的时钟源进行切换,也可以避免亚稳态的产生。 从上图中第二个箭头开始,实际发生时钟切换。

CLK0与CLK1为无关时钟源,即异步时钟源在第一种方法的基础上,在选择路径上再插入一个上升沿触发D触发器,这是对异步信号进行同步处理,这样即使是两个异步的时钟源进行切换,也可以避免亚稳态的产生。 从上图中第二个箭头开始,实际发生时钟切换。

两种做法都会产生时钟切换毛刺的,芯片系统很容易进入亚稳态的情况。

两种做法都会产生时钟切换毛刺的,芯片系统很容易进入亚稳态的情况。 为了解决时钟切换的毛刺问题,对于时钟源分为同步和异步的情况,分为如下两种解决方案:CLK0与CLK1为同步时钟源,即CLK0与CLK1成整数倍关系:插入下降沿触发的D触发器,当前已打开的时钟路径上的时钟会在其下降沿之后先关闭,然后待打开时钟路径上的时钟在其下降沿之后即打开。如下所示:从下图第二个箭头开始,实际发生时钟切换。

为了解决时钟切换的毛刺问题,对于时钟源分为同步和异步的情况,分为如下两种解决方案:CLK0与CLK1为同步时钟源,即CLK0与CLK1成整数倍关系:插入下降沿触发的D触发器,当前已打开的时钟路径上的时钟会在其下降沿之后先关闭,然后待打开时钟路径上的时钟在其下降沿之后即打开。如下所示:从下图第二个箭头开始,实际发生时钟切换。 CLK0与CLK1为无关时钟源,即异步时钟源在第一种方法的基础上,在选择路径上再插入一个上升沿触发D触发器,这是对异步信号进行同步处理,这样即使是两个异步的时钟源进行切换,也可以避免亚稳态的产生。 从上图中第二个箭头开始,实际发生时钟切换。

CLK0与CLK1为无关时钟源,即异步时钟源在第一种方法的基础上,在选择路径上再插入一个上升沿触发D触发器,这是对异步信号进行同步处理,这样即使是两个异步的时钟源进行切换,也可以避免亚稳态的产生。 从上图中第二个箭头开始,实际发生时钟切换。

转载:全栈芯片工程师

免责声明:文章内容来自互联网,本站不对其真实性负责,也不承担任何法律责任,如有侵权等情况,请与本站联系删除。

转载请注明出处:时钟切换clk_switch-verilog时钟翻转 https://www.yhzz.com.cn/a/11197.html