在8B/10B、64B/66B编解码(二)一文中,提到了GearBox的运用,本文聊聊GearBox的设计原理。譬如10GBase-R协议中规定64bit数据经过66B编码、扰码后的数据变成64bit的有效数据、2bit的同步头,而Serdes的并行端数据输入的位宽数可能是8bit、10bit、16bit、32bit等等小于66bit的位宽,因此芯片发送数据到Serdes模块时需要进行位宽大到小的转换。同样,芯片从Serdes模块接收数据时,也需要完成数据位宽由小到大的转变。GearBox就是实现任意数据位宽之间转换的变速箱。关于编码过程,参考如下例子:

为了说明GearBox原理,上述例子给的很简单,而实际是非常复杂的,比如下面例子:在IEEE802.3协议中,规定了MAC层、PCS层的结构,说明了MII接口的位宽和时钟频率,但是实际verilog实现中,MAC/PCS的时钟常常与协议不一致。如下图所示,以发送方向为例,数据经过MAC_TX、PCS_TX、通过serdes传输到对端。常见速率设计方法是:mac tx的极限速率>=pcs tx的极限速率>serdes的速率。此结构为漏斗型,数据上游的带宽大,数据下游的带宽小,采用ram和afifo实现数据的转换,逐级反压流控,由下游带宽决定实际速率。

为了说明GearBox原理,上述例子给的很简单,而实际是非常复杂的,比如下面例子:在IEEE802.3协议中,规定了MAC层、PCS层的结构,说明了MII接口的位宽和时钟频率,但是实际verilog实现中,MAC/PCS的时钟常常与协议不一致。如下图所示,以发送方向为例,数据经过MAC_TX、PCS_TX、通过serdes传输到对端。常见速率设计方法是:mac tx的极限速率>=pcs tx的极限速率>serdes的速率。此结构为漏斗型,数据上游的带宽大,数据下游的带宽小,采用ram和afifo实现数据的转换,逐级反压流控,由下游带宽决定实际速率。

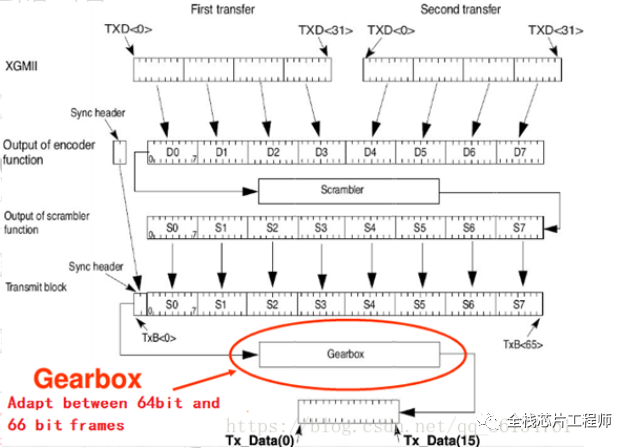

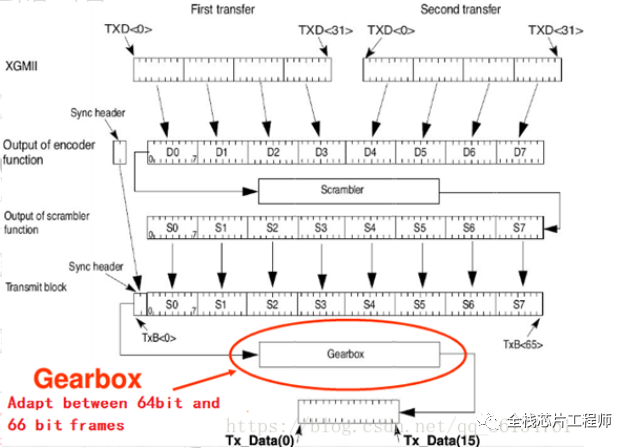

若从物理编码子层XGMII传来两个32bit,加在一起64bit,经过encoder进行编码,得到编码后的数据D0-D7,生成同步头01。

然后,不含同步头的D0-D7,经过扰码器,得到表达式X58+X39+1扰码后的数据S0-S7。之后,将同步头和扰码后的数据S0-S7合并,生成一个传输块,将这个传输块经过GearBox处理后,完成编码。接下来具体说明变速箱GearBox的实现过程,以10GBase-R的物理层为例,若Serdes的位宽要求为32bit,PCS层采用64B/66B的编解码方式,在与Serdes进行数据传输过程中,需要GearBox实现66bit到32bit的转换、32bit到66bit的转换。继续以上图为例子,XGMII层每拍输出32bit数据,每2拍组合成64bit报文,并且需要编码出2bit的同步头,为了简单化,假设待匹配的Serdes只有1个lane,且位宽为32bit,即GearBox输出是每拍32bit。显然,输入带宽是大于输出带宽,属于带宽膨胀,因此输入必须暂停,什么时候停呢,见下图波形所示,每32拍停一拍,即待发送的buffer数据积攒够了32bit,此时,产生暂停输入标志位,也就是“反压”住输入信号,让GearBox可以完成数据完整输出。PS:下图计数器计到31即可。 为了说明GearBox原理,上述例子给的很简单,而实际是非常复杂的,比如下面例子:在IEEE802.3协议中,规定了MAC层、PCS层的结构,说明了MII接口的位宽和时钟频率,但是实际verilog实现中,MAC/PCS的时钟常常与协议不一致。如下图所示,以发送方向为例,数据经过MAC_TX、PCS_TX、通过serdes传输到对端。常见速率设计方法是:mac tx的极限速率>=pcs tx的极限速率>serdes的速率。此结构为漏斗型,数据上游的带宽大,数据下游的带宽小,采用ram和afifo实现数据的转换,逐级反压流控,由下游带宽决定实际速率。

为了说明GearBox原理,上述例子给的很简单,而实际是非常复杂的,比如下面例子:在IEEE802.3协议中,规定了MAC层、PCS层的结构,说明了MII接口的位宽和时钟频率,但是实际verilog实现中,MAC/PCS的时钟常常与协议不一致。如下图所示,以发送方向为例,数据经过MAC_TX、PCS_TX、通过serdes传输到对端。常见速率设计方法是:mac tx的极限速率>=pcs tx的极限速率>serdes的速率。此结构为漏斗型,数据上游的带宽大,数据下游的带宽小,采用ram和afifo实现数据的转换,逐级反压流控,由下游带宽决定实际速率。

如图所示,图中以4 lane serdes实现公共200G速率,每lane serdes在528FEC/NOFEC模式下的极限速率是51.5625G,serdes数据位宽为80bit,serdes恢复时钟serdes_twclk为644.53125MHz。Mac tx模块生成4路MII接口,pcs_tx模块包含pcs层和fec的处理,输出80bit的并行数据送到serdes。

Serdes的速率控制实在gearbox模块实现的,gearbox模块主体存储结构是位宽为80的afifo,读侧采用serdes恢复时钟serdes_twclk,每个时钟周期读取一个数据,实际速率为80bit*644.53125MHz=51.5625Gbps,由于pcs tx的极限速率大于51.5625,所以gearbox模块的内部afifo一直不会空,当afifo内部数据超过阈值时会向上游起反压流控,暂停数据下发,防止afifo溢出,阈值设置要合理,要防止下游断流。Gearbox模块写侧时钟为pcs_clk,pcs_clk需要大于serdes_twclk才能保证afifo一直有数据。Mac_tx模块的极限带宽计算为4*64*mac_clk,要大于200G,因此mac_clk不能低于781.25Mhz,保证mac tx的极限速率>=pcs tx的极限速率>serdes的速率,因此mac_clk可以选择在800MHz~900Mhz,pcs_clk可以选择在mac_clk~700Mhz之间,pcs_clk也可以选择与mac_clk同一个时钟,这样可以减少跨时钟设计。可以看到,在很简单的情况下,GearBox仅需完成诸如66bit<->32bit的位宽转换,甚至不涉及跨时钟设计。而在复杂系统下,GearBox需要有位宽转换、async_fifo数据缓存,涉及到了afifo水线设置、反压、输入输出带宽匹配、fifo深度等等问题。感谢阅读文章,如果文章有用,麻烦点个“在看”或转发分享。

转载:全栈芯片工程师

免责声明:文章内容来自互联网,本站不对其真实性负责,也不承担任何法律责任,如有侵权等情况,请与本站联系删除。

转载请注明出处:详解GearBox设计原理-gearbox 游戏 https://www.yhzz.com.cn/a/11183.html