dbGet

[-p num ]

[-u]

[-regexp]

[-d]

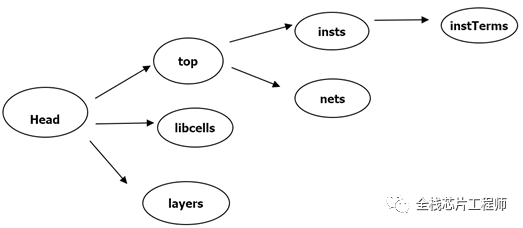

{ obj | objList | head | top | selected}

[. objType ]…[. attrName | .? | .?? |.?h]

[ pattern ]

[expression]

[-v]

[-e]

[-i] -p是我们经常用到的option。p指point,有时我们使用dbGet筛选得到我们所想要的结果。但更多时候,这些结果会被用来做另一个层级的dbGet指令。这时候就要用到-p,来返回指针。如果我们想要知道所有在M3上的insts pin的名字:

innovus 59> dbGet [dbGet -p2 top.insts.instTerms.layer.name M3].name

CHIP_TOP/buf_input_datax2x/AREPEATER_datax2x/Z ……

给出几个例子:

列出设计中所有place/unplace的instance

dbGet [dbGet -p top.insts.pStatus unplaced].namedbGet [dbGet -p top.insts.pStatus placed].nameList all fixed instances in the designdbGet [dbGet -p top.insts.pStatus fixed].nameList the metal layers on which the I/O pins of the block reside

dbGet top.terms.pins.allShapes.layer.name获得所有 spare instances

dbGet [dbGet -p top.insts.isSpareGate 1].nameget 特定instance的pg pin

dbGet [dbGet top.insts.name $instName -p ].pgInstTerms.nameCadence提供了更为详细的命令,参考如下:You can use the following single-line dbGet scripts to explore various aspects of your design:

List all unplaced instances in the design

dbGet [dbGet -p top.insts.pStatus unplaced].nameList all placed instances in the design

dbGet [dbGet -p top.insts.pStatus placed].nameList all fixed instances in the design

dbGet [dbGet -p top.insts.pStatus fixed].nameList the metal layers on which the I/O pins of the block reside

dbGet top.terms.pins.allShapes.layer.nameList the non default rules (NDR) in the design

dbGet head.rules.nameList the NDRs applied on a specified net

dbGet [dbGet -p top.nets.name netName].rule.nameList net names with specific max or min voltage

dbGet [dbGet top.nets.maxVoltage value –p].name dbGet [dbGet top.nets.minVoltage value –p].nameGet the placement status of an instance

dbGet [dbGetInstByName instName].pStatusTo avoid splitting of a specified multibit flop, during multibit Optimization

dbSet [dbGetInstByName ].dontSplitMultibit 1To avoid merging of a specified multibit flop, during multibit Optimization

dbSet [dbGetInstByName ].dontMergeMultibit 1Get the coordinates of a rectangular routing blockage

dbGet top.fplan.rBlkgs.shapes.rectGet the coordinates of a rectilinear routing blockage

dbGet top.fplan.rBlkgs.shapes.polyList all cell types used in the design

dbGet -u top.insts.cell.nameNote: The “-u” parameter filters out the duplicate objects.

Get the size of block placement halos

dbGet [dbGet -p2 top.insts.cell.subClass block*].pHaloTop dbGet [dbGet -p2 top.insts.cell.subClass block*].pHaloBot dbGet [dbGet -p2 top.insts.cell.subClass block*].pHaloLeft dbGet [dbGet -p2 top.insts.cell.subClass block*].pHaloRightGet the size and top/bottom layers of block routing halos

dbGet [dbGet -p2 top.insts.cell.subClass block*].rHaloSideSize dbGet [dbGet -p2 top.insts.cell.subClass block*].rHaloBotLayer.name dbGet [dbGet -p2 top.insts.cell.subClass block*].rHaloTopLayer.nameEnsure all your tiehi/tielo connections have tie cells (and are not connected to a rail instead)

dbGet top.insts.instTerms.isTieHi 1dbGet top.insts.instTerms.isTieLo 1The previous commands should return “0x0” if all connections have tie cells. If “1s” are returned, use the following commands to find the terms that still need a tie cell:dbGet [dbGet -p top.insts.instTerms.isTieHi 1].namedbGet [dbGet -p top.insts.instTerms.isTieLo 1].nameGet all instTerm names that are tied to tieLo cells

dbGet [dbGet -p [dbGet -p2 top.insts.cell.subClass coreTieLo].instTerms.net.allTerms.isInput 1].nameChange the routing status of a net (for example, from FIXED to ROUTED)

dbSet [dbGet -p top.nets.name netName].wires.status routeGet the status of the design

dbGet top.statusIoPlaced dbGet top.statusPlaced dbGet top.statusClockSynthesized dbGet top.statusRouted dbGet top.statusRCExtracted dbGet top.statusPowerAnalyzedList the layers used in a net

dbGet [dbGet -p top.nets.name netName].wires.layer.nameSelecting Shield Nets of a net

dbSelectObj [dbget [dbget -p [dbGet -p top.nets.name $net].shieldNets.name GND].sWires.shieldNet.name $net -p2]NOTE: $net is the net for which you want to select the shield.

Find all instances of a certain cell type

dbGet [dbGet -p2 top.insts.cell.name cellName].nameDetermine the size of a cell in the library, but not necessarily in the current design

dbGet [dbGetCellByName cellName].sizeList the nets marked in the db as clock net

dbGet [dbGet -p top.nets.isClock 1].nameNote: Before running the previous command, build a timing graph using the timeDesign command.

Set all instances with a particular pattern in the name to fixed status

dbSet [dbGet –p top.insts.name *clk*].pStatus fixedGet top and bottom routing layers for a route_type

dbGet [dbGet -p head.routeTypes.name routeTypeName].topPreferredLayer.num dbGet [dbGet -p head.routeTypes.name routeTypeName].bottomPreferredLayer.numGet database units

dbGet head.dbUnitsGet the manufacturing grid

dbGet head.mfgGridGet physical only cells such as filler cell, end cap cell, and so on

dbGet [dbGet -p top.insts.isPhysOnly 1].nameReport Dont Touch instances:

dbGet [dbGet -p top.insts.dontTouch true].nameReport Dont Use cells in the database

dbGet [dbGet -p head.libCells.dontUse 1].nameReport JTag elements:

dbGet [dbGet -p top.insts.isJtagElem 1].nameReport spare instances:

dbGet [dbGet -p top.insts.isSpareGate 1].nameFilter all PG pins with direction bidi of a specific instance

dbGet [dbGet -p [dbGet -p top.insts.name instName].pgCellTerms.inOutDir bidi].nameGet PG pins connections of a specific instance

proc getInstPGConnect {c} { set inst [dbget -p top.insts.name $c] puts “PG connection of instance $c:” foreach PGT [dbget $inst.pgCellTerms.name] { puts “\tPin : $PGT –> Net: [dbget [dbPGTermNet [dbGetPGTermByName $inst $PGT]].name]” } }Get class and subClass of a cell

dbGet [dbGetCellByName cellName].baseClass dbGet [dbGetCellByName cellName].subClassSelecting all Macros/Blocks of a particular module (or Hierarchical instance)

selectInst [dbGet [dbGet top.hInst.allTreeInsts.cell.baseClass block -p2].name <specify_module_name> ]Get all the sequential cells of a particular module

selectModule <module_name> dbGet [dbGet selected.insts.cell.isSequential 1 -p2].nameGet the instname / cellname of the driver driving a specific net

set netName netName set inst [dbGet [dbGet -p [dbGet -p top.nets.name $netName].allTerms.isOutput 1].inst] Puts “Net: $netName, driving inst name: [dbGet $inst.name], driving cell name: [dbGet $inst.cell.name]”List all layers for the pin of a cell

dbGet [dbGet -p selected.cell.terms.name pinName].pins.allShapes.layer.extNameReport points of the polygon that forms the die area

dbShape -output polygon [dbGet top.fPlan.boxes]Get Verilog module ports

dbGet [ dbGet -p1 top.hInst.allTreeInsts.name $moduleInstName].hInstTerms.hTerm.nameTo query top level term pin coordinates and layer number

lindex [dbGet [dbGet top.hinst.hinstTerms.term.name – p].pins.allShapes.shapes.rect] 0 dbGet [dbGet top.hinst.hinstTerms.term.name -p].pins.allShapes.layer.numQuery max_cap for a list of cells

cellPtrList [dbGet -p head.allCells.n ame BUF*] foreach cellPtr $cellPtrList {puts “[dbGet $cellPtr.name] [dbFTermMaxCap [dbGet -p $cellPtr.terms.name termName] 1]”}Find all instances with a specify property name “myProp” (string property type) and value “xyzzy”

set inst_ptrs [dbGet -p top.insts.props {.name == “myProp” && .value == “xyzzy”]Puts “Instances with property myProp and value xyzzy: [dbGet $inst_ptrs.name]”Find non-clock ports in a design

dbGet [dbGet -p [dbGet -p2 top.terms.net.isClock 0].isInput 1].nameTo get information on all tech sites in the design

dbGet head.sites.name dbGet head.sites.size dbIsTechSiteVDDOnBottom [dbGet head.sites.name -p]Identify and report ‘physical only’ types of cells (well tap, tie hi/lo, filler, endcap/decap)

You can query the subclass for a cell to check whether it is welltap, tiehigh, tielow or end cap:

dbGet [dbGet -p head.libCells.subClass ].name For example, to get names of well tap cells (specified as ‘CLASS CORE WELLTAP ‘ in LEF), you can use the following command:dbGet [dbGet -p head.libCells.subClass coreWellTap].nameSimilarly, to get names of tie high / tie low cells (specified as ‘CLASS CORE TIEHIGH’ or ‘CLASS CORE TIELOW’ in LEF), use the following command:dbGet [dbGet -p head.libCells.subClass coreTieHigh].nameORdbGet [dbGet -p head.libCells.subClass coreTieLow].nameTo report endcap cells (specified as ‘CLASS ENDCAP’ in LEF), use the following command:dbGet [dbGet -p head.libCells.subclass coreEndCap*].nameSimilarly, to query filler cells with ‘CLASS CORE SPACER’ in the LEF syntax, you can use the following command (similar to other physical-only cells): dbGet [dbGet -p head.libCells.subClass coreSpacer].namePrint all module names in the design

foreach module_name [dbGet top.hInst.treeHInsts.cell.name] { Puts “$module_name“ }This will not include the top module name. To get the top module name, run the following command:

dbGet top.nameGet all leaf cells used in the design

foreach leaf_name [dbGet -u top.insts.cell.name] { Puts “$leaf_name“ }Apply set_dont_touch on selected instances

Select the instances on which to apply set_dont_touch. For example, select all level-shifter instances with the “LS” prefix:

dbGet top.insts.name LS*Then, run the following command:foreach term [dbGet selected.instTerms.net.term –e] { set_dont_touch [dbGet $term.net.name] true }Skip routes hierarchical hard macro nets

proc skiproutesOnHmsNets {hmInstPattern} { deselectAll selectInst *$hmInstPattern* dbset selected.hinst.hnets.net.skipRouting 1 deselectAll }Removing nets over the Macros along with pitches and vias

Incase some nets are routed over the Hard Macros, you can remove such nets along with pitches and vias using following command:

foreach c [dbGet [dbGet -p2 top.insts.cell.baseClass block].name] { set j [dbGet -p top.insts.name $c ] dbSelectObj [dbQuery -area [dbGet $j.box ] -objType regular] puts “Deleting object at [dbGet $j.box ] within Block [dbget $j.name]” editDelete -selected –type Signal -use SIGNAL }Get the number of vias that are not power in a routed design

llength [dbGet [dbGet -p top.nets.isPwrOrGnd 0].vias]Break the DFM flow if metal fills are not added to design using run_pvs_metal_fill.

Include following set of command to break the script if metal fill is not added to design

puts “Checking if run_pvs_metal_fill successfully inserted metal fill shapes…”

if {[dbGet [dbGet -p top.nets.name _FILLS_RESERVED].sWires.shape fillwire] >= 0} { puts “db has metal fill – continuing…” set has_fill 1 } else { puts “db has no metal fill – stopping dfm run…” set has_fill 0 }if {$has_fill < 1} { break } else { .. < rest of of your script>Report instance pin shape mask

You can use TCL procedure below to report the mask(color) of the instance pin:

proc pinColor {instPin layer} { if {![regexp $layer [dbGet [dbGet top.insts.instTerms.name $instPin -p].cellTerm.pins.allShapes.layer.name]]} { Puts “$instPin doesnt have pin shape on $layer“ } else { dbGet [dbGet [dbGet top.insts.instTerms.name $instPin -p].cellTerm.pins.allShapes.layer.name $layer -p2].shapes.mask } }pinColor Ainst/o VIA1Report latency of all memories in the design

Following script prints the latency of all memories with cell name *RAM* and clock pin name *CLK. You can change *RAM* with cell name of the desired memories, or as per your design.

set mem_pin [dbget [dbget top.insts.cell.name *RAM* -p2].instTerms.name *CLK] foreach i $mem_pin { puts “$i [get_property [get_pins $i] actual_latency_late_rise_max]” }Report all flop instances with reset pin connected to the supply

# dentify all flops with reset tied directly to the vss rail # report total count, and each instname and cellname to an # output file named flop_with_tied_rst.rptproc findRstPinsTiedToRail{ $VSS_name $RSTport } { # dont echo dbGet, etc. to screen/log: setPreference CmdLogMode 1 # output file name: set ofile “flop_with_tied_rst.rpt” set ecofp [ open $ofile w ] set cnt [llength [dbGet [dbGet [dbGet top.nets.name $VSS_name -p].instTerms.cellTerm.name $RSTport -p2 ].inst.name ]] set insts [dbGet [dbGet [dbGet top.nets.name $VSS_name -p].instTerms.cellTerm.name $RSTport -p2 ].inst ] set cnt2 [llength $insts] puts $ecofp “Total: $cnt $cnt2“ #foreach inst_ptr [dbGet [dbGet [dbGet top.nets.name $VSS_name -p].instTerms.cellTerm.name $RSTport -p2 ].inst ] foreach inst_ptr $insts { set inst_name [dbGet $inst_ptr.name] set cell_ptr [dbInstCell $inst_ptr] set cell_name [dbGet $cell_ptr.name] set rst_port [dbGet $inst_ptr.instTerms.cellTerm.name $RSTport -p2] set net [dbGet $rst_port.net.name] puts $ecofp “$inst_name $cell_name “ } close $ecofp }To get the status of a design:

encounter> dbGet top.?? status* // reports the list of status at particular stage statusClockSynthesized: 0 statusGRouted: 0 statusIoPlaced: 1 statusPlaced: 1 statusPowerAnalyzed: 0 statusRCExtracted: 0 statusRouted: 1 statusScanOpted: 0Example to check a particular value:encounter> dbGet top.statusPlaced 1 // it shows design is placedNote: The top.statusClockSynthesized flag is only for FE-CTS [setCTSMode -engine ck] not for CCOpt.

Create SDP(structured data path) groups of clock gates and flops:

The following script will find the clock gates and the flops connected to the clk pin in the design and group them together using createSdpGroup

Script:

set clock_gates [dbget [dbget top.insts.cell.name *cgc* -p2].instTerms.name *clk -p2] foreach i $clock_gates { ## find clock net of the clock gate set clock_net [dbget $i.instTerms.name *clk -p] set sdp_group_name [string map {/ _} [join [dbget $i.name] “”]] set flops [dbget [dbget $clock_net.net.instTerms.isInput 1 -p].inst.name ] createSdpGroup -name $sdp_group_name -alignByPinName clk -inst $flops}

Note: Please use cell name and clock pins name(cgc and clk used for example) as per the library specifications.

转载:全栈芯片工程师

免责声明:文章内容来自互联网,本站不对其真实性负责,也不承担任何法律责任,如有侵权等情况,请与本站联系删除。

转载请注明出处:innovus dbGet命令的使用-get_dbsize_info https://www.yhzz.com.cn/a/11048.html