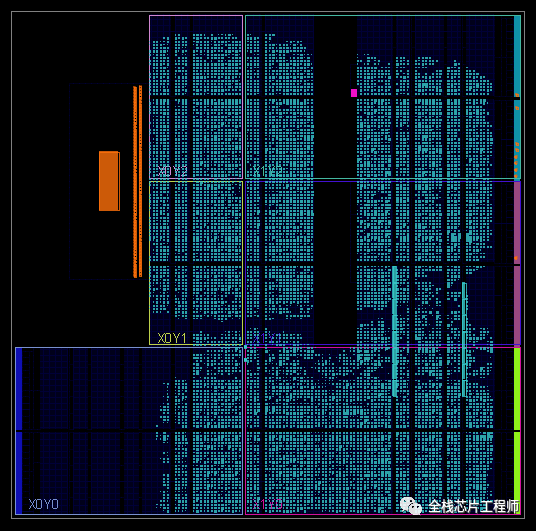

从芯片设计/实现工程师的角度看FPGA是如何将“超前进位加法器”的RTL代码进行逻辑综合、布局布线实现。FPGA 主要有六部分组成:可编程输入输出单元(IO)、可编程逻辑单元(CLB)、完整的时钟管理、嵌入块状RAM、布线资源、内嵌的底层功能单元和内嵌专用硬件模块。其中最为主要的是可编程输出输出单元、可编程逻辑单元和布线资源。如下图,最左边橘色方块是PS7,即ARM-Cortex A9双核处理器,其右边橘色两列是IO,其余绝大部分是CLB(Configurable Logic Block)、以及BRAM、DSP等等资源。

首先我们来看Xilinx ZYNQ-7000的底层结构,可配置逻辑单元CLB (Configurable Logic Block)是FPGA 中最为丰富的资源,我们重点看看可配置逻辑单元CLB。

布局用到的LUT、Flip-Flop呈现高亮颜色,下图可以看见,设计绝大部分用的都是LUT和Flip-Flop。

CLB由两个SLICE组成,每个SLICE包含LUT查找表、Flip-Flop、进位链、MUX。如下图SLICE结构,布局用到的3个LUT、2个Flip-Flop呈现高亮颜色。简而言之,可配置逻辑单元CLB包含如下:6 输入查找表(LUT6)

选择器(MUX)

进位链(Carry Chain)

触发器(Flip-Flop)

LUT6的结构如下:

一方面,LUT6可作为64×1的ROM使用;一方面,LUT6可作为分布式RAM使用,写同步,而读操作是直接译码输出,为了到底同步效果,可以利用SLICE的Flip-Flop打一拍输出,完成时序收敛。我们再看看Routing Resources:局部放大看看:

仔细看下图SLICE的器件、绕线的利用情况,可以发现:

LUT6作为组合逻辑使用;Flip-Flop作为时序逻辑使用;使用了的绕线资源显示为绿色,未使用的绕线显示为灰色。 下文我们将重点介绍Xilinx FPGA中的进位链,根据进位链来实现加法、减法运算,其内部含4个MUX、4个2输入异或门(XOR),异或运算是加法运算中必不可少的。先思考下,如果自己的大脑是EDA工具,如何利用上图进位链的单元实现超前进位加法呢?

时间原因,根据进位链来实现“超前进位加法器”的具体剖析见下文。

感谢阅读文章,如果文章有用,麻烦点个“在看”或转发分享。

转载:全栈芯片工程师

免责声明:文章内容来自互联网,本站不对其真实性负责,也不承担任何法律责任,如有侵权等情况,请与本站联系删除。

转载请注明出处:剖析FPGA怎么实现“超前进位加法器”(一)-超前进位加法器和串行进位加法器 https://www.yhzz.com.cn/a/10792.html