1 滤波器的特征参数介绍

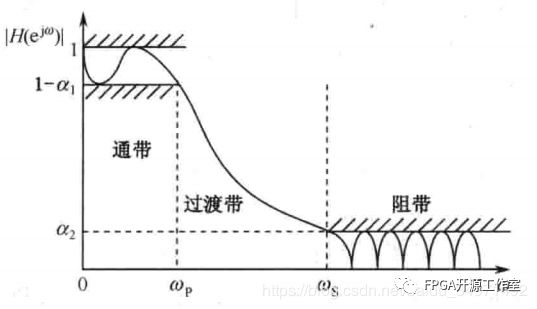

图1 低通滤波器特征参数 如图1所示,低通滤波器的通带截止频率为ωp ,通带容限为α1,阻带截止频率为ωs,阻带容限为α2。通带定义为|ω|≤ωp ,过渡带定义为ωp<|ω|<ωs,阻带定义为ωs≤|ω|<π。2 设计目标

要求:使用fir滤波器设计一个滤波器系数为15阶的低通滤波器,通带截止频率为1KHZ,采样频率为44.1khz。

3 matlab的设计验证

close all

clear all

clc

%设计一个低通滤波器 采样频率为44.1khz, 截止频率为1khz

FS = 44100; %HZ

fc = 1000;

N = 15;

Q = 16;

%以采样频率的一半,对频率进行归一化处理

wn_lpf=fc*2/FS;

%采用fir1函数设计FIR滤波器

b_lpf=fir1(N-1,wn_lpf);

%滤波系数进行量化

b_16=round(b_lpf/max(abs(b_lpf))*(2^(Q-1)-1));

%求滤波器的幅频响应

m_lpf=20*log(abs(fft(b_lpf)))/log(10);

b16_lpf=20*log(abs(fft(b_16)))/log(10);

%设置幅频响应的横从标单位为Hz

x_f=[0:(FS/length(m_lpf)):FS/2];

%绘制单位脉冲响应

subplot(221);stem(b_lpf);xlabel(n);ylabel(h(n));

title(低通滤波器的单位脉冲响应,fontsize,8);

subplot(222);stem(b_16);xlabel(n);ylabel(h(n));

title(低通滤波器的单位脉冲响应,fontsize,8);

%绘制幅频响应曲线

subplot(223);plot(x_f,m_lpf(1:length(x_f)));xlabel(频率(Hz),fontsize,8);ylabel(幅度(dB),fontsize,8);

title(低通滤波器的幅频响应,fontsize,8);

subplot(224);plot(x_f,b16_lpf(1:length(x_f)));xlabel(频率(Hz),fontsize,8);ylabel(幅度(dB),fontsize,8);

title(低通滤波器的幅频响应,fontsize,8);

4 FPGA信号发生器

为了验证低通滤波器,我们设计了测试验证的sin信号发生器。

wire [17:0] kfreq= (k<2048)?18’h00333:18’h00FFF;//1khz-5khz

产生1khz和5khz的sin波。

图3 信号发生器产生1khz和5khz的sin测试源

图3 信号发生器产生1khz和5khz的sin测试源测试源的FFT分析:

图4 测试源数据的matlab分析

图4 测试源数据的matlab分析

由图4的频域图可知,测试源产生了1khz和5khz的sin。

5 FPGA的fir设计

Fir滤波器verilog代码设计采取全并行模式。

`timescale 1ps/1ps

module fir1( input mclk,//45.1584MHZ input reset_n, input signed[31:0] pcm_in, output signed[31:0]pcm_out

);localparam LAST_CYCLE = 1023;reg [9:0] i;reg signed [31:0] pcm1,pcm2,pcm3,pcm4,pcm5,pcm6,pcm7,pcm8,pcm9,pcm10,pcm11,pcm12,pcm13,pcm14,pcm15;reg signed [47:0] pcm1_out,pcm2_out,pcm3_out,pcm4_out,pcm5_out,pcm6_out,pcm7_out,pcm8_out,pcm9_out,pcm10_out,pcm11_out,pcm12_out,pcm13_out,pcm14_out,pcm15_out;reg signed [51:0] pcm_r;wire signed [15:0] coeff1,coeff2,coeff3,coeff4,coeff5,coeff6,coeff7,coeff8,coeff9,coeff10,coeff11,coeff12,coeff13,coeff14,coeff15;assign coeff1 = 2208;assign coeff2 = 3631;assign coeff3 = 7612;assign coeff4 = 13576;assign coeff5 = 20413;assign coeff6 = 26727;assign coeff7 = 31169;assign coeff8 = 32767;assign coeff9 = 31169;assign coeff10 = 26727;assign coeff11 = 20413;assign coeff12 = 13576;assign coeff13 = 7612;assign coeff14 = 3631;assign coeff15 = 2208;assign pcm_out = pcm_r[51:20];always @(posedge mclk or negedge reset_n)begin

if(!reset_n)begin

i<= 0; pcm1<=0; pcm2<=0; pcm3<=0; pcm4<=0; pcm5<=0; pcm6<=0; pcm7<=0; pcm8<=0; pcm9<=0; pcm10<=0; pcm11<=0; pcm12<=0; pcm13<=0; pcm14<=0; pcm15<=0; pcm1_out<=0; pcm2_out<=0; pcm3_out<=0; pcm4_out<=0; pcm5_out<=0; pcm6_out<=0; pcm7_out<=0; pcm8_out<=0; pcm9_out<=0; pcm10_out<=0; pcm11_out<=0; pcm12_out<=0; pcm13_out<=0; pcm14_out<=0; pcm15_out<=0; pcm_r<= 0;end

elsebegin

i <= i + 1; if(i == 0)begin

pcm1<=pcm_in; pcm2<=pcm1; pcm3<=pcm2; pcm4<=pcm3; pcm5<=pcm4; pcm6<=pcm5; pcm7<=pcm6; pcm8<=pcm7; pcm9<=pcm8; pcm10<=pcm9; pcm11<=pcm10; pcm12<=pcm11; pcm13<=pcm12; pcm14<=pcm13; pcm15<=pcm14;end

if(i==1)begin

pcm1_out <= pcm1*coeff1; pcm2_out <= pcm2*coeff2; pcm3_out <= pcm3*coeff3; pcm4_out <= pcm4*coeff4; pcm5_out <= pcm5*coeff5; pcm6_out <= pcm6*coeff6; pcm7_out <= pcm7*coeff7; pcm8_out <= pcm8*coeff8; pcm9_out <= pcm9*coeff9; pcm10_out <= pcm10*coeff10; pcm11_out <= pcm11*coeff11; pcm12_out <= pcm12*coeff12; pcm13_out <= pcm13*coeff13; pcm14_out <= pcm14*coeff14; pcm15_out <= pcm15*coeff15;end

if(i==2) pcm_r<= pcm1_out +pcm2_out+pcm3_out+pcm4_out+pcm5_out+pcm6_out+pcm7_out+pcm8_out+pcm9_out+pcm10_out+pcm11_out+pcm12_out+pcm13_out+pcm14_out+pcm15_out;end

end

endmodule

fpga实验modelsim仿真结果,从图5来看1khz几乎保持不变,而5khz波形幅度上被抑制了很多。

图5 modelsim fir实验结果时域波形

图5 modelsim fir实验结果时域波形

Matlab fft分析:

图6 matlab分析实验结果

图6 matlab分析实验结果由图2和图6对比,5khz经过滤波后的功率减小了20DB,图2与图5基本一致,fir的低通滤波器全并行设计成功。

感谢阅读,别走!点赞、关注、转发后再走吧

转载:全栈芯片工程师

免责声明:文章内容来自互联网,本站不对其真实性负责,也不承担任何法律责任,如有侵权等情况,请与本站联系删除。

转载请注明出处:低通滤波器的FIR的设计-低通滤波器fp https://www.yhzz.com.cn/a/10646.html