Standard Cell Architecture

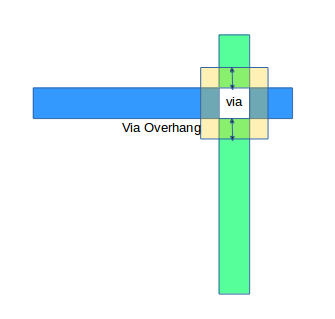

●Standard cells are designed based on power, area and performance.●First step is cell architecture. Cell architecture is all about deciding cell height based on pitch & library requirements. We have to first decide the track, pitch, β ratio, possible PMOS width and NMOS width.●Track : Track is generally used as a unit to define the height of the std cell.Track can be related to lanes e.g. like we say 4 lane road, implies 4 vehicles can run in parallel. Similarly, 9 track library implies 9 routing tracks are available for routing 9 wires in parallel with minimum pitch.●Pitch : The distance between two tracks is called as pitch.●Via : Vias are used to connect two different metal layers as shown in Fig. 1(a). In Fig.1(b), we are connecting M1 and M2 using a Via. We don’t make tracks with minimum spacing as we will get DRC error if there is any via overhang. Fig. 1(a) Via connecting metal 1 and metal 2.

Fig. 1(a) Via connecting metal 1 and metal 2. Fig. 1(b) Pitch calculation including via overhang● Let us see how to calculate the standard cell height, pitch, size of PMOS and NMOS for a 9 track library.

Fig. 1(b) Pitch calculation including via overhang● Let us see how to calculate the standard cell height, pitch, size of PMOS and NMOS for a 9 track library.

Let the metal width be 4 units, minimum metal to metal spacing is 3 units and via overhang be 2.

Pitch = 2[1/2(metal width)+Via overhang]+ metal-to-metal spacing. Using this formula, Pitch = 11 units.

Standard cell height = Pitch * (N-1) where N represents the number of tracks. This sums to 88 units.

In a layout, the cells will be arranged one above the other, in such away that they can share one common VDD and VSS. Fig. 2 depicts two cells(can be any cells) abutted in such a way that they share the same VDD.

Fig. 2 Calculation of Standard cell height

Fig. 2 Calculation of Standard cell height

● Let us take the β ratio as 1.5. Hence, Wp=1.5Wn. Below given are the variables used for calculating the standard cell height :

p = Poly overhang, here it is 2 units.

x = Minimum well to well spacing required between the two cells, here it is 12 units.y = We need to leave half of the space between corresponding layer to avoid half DRC violation between two different cells abutted on VDD and VSS. This comes to 1.5 units.Wp = Width of PMOS.Wn = Width of NMOS.● Height of the standard cell , Wp+Wn+x+2y+2p = 88 units.●Using this formula, Wn is calculated as 27.6 units and Wp is calculated as 41.4 units. Similarly we can calculate Wn and Wp values for different libraries.●If we compare 7T and 11T, 11T is faster and will give better performance because the area for 11T is more so that we can place higher drive strength transistors in it.

Using 11T library we can achieve higher utilizations.11T library are used for better performance.7T library are used for higher density & low power.Cells in generic library1. Basic gates (AND, OR, NAND, NOR, INV, EXOR, EXNOR)2. MUX3. HA, FA4. Special cells (Fillers, Tap cells, End Cap, De Caps)5. Tie Cells6. Metal Eco-able cells7. AOI8. OAI9. Boolean function cells10. Flops (Normal D flip flop, Scan-able flop with set / reset)11. Clock gate原文链接:https://mp.weixin.qq.com/s/91uIeOu6Q1MuJuJiZ5OFjg

感谢阅读,别走!点赞、关注、转发后再走吧

转载:全栈芯片工程师

免责声明:文章内容来自互联网,本站不对其真实性负责,也不承担任何法律责任,如有侵权等情况,请与本站联系删除。

转载请注明出处:标准单元库设计(一)-标准单元设计方法 https://www.yhzz.com.cn/a/10432.html