在公众号后台回复:220327,获取手把手教你学ARM_FPGA教程。

在公众号后台回复:220318,获取以上文件的下载地址。

Cortex-M3软核IP下载地址:

Cortex-M3 DesignStart FPGA-Xilinx edition(r0p1-00rel0)

https://silver.arm.com/browse/AT426

文件名称:AT426-BU-98000-r0p1-00rel0.tgz

需要注册ARM官网账号,填写一些信息后才能下载。也可以关注我的公众号,在公众号后台回复:220318,获取以上文件的下载地址。

文件名称:Cortex-M3 DesignStart FPGA-Xilinx edition(r0p1-00rel0)

文件大小:7.52MB

MD5SUM:cd67536c29023429cde47130d51b6f49

2010年,ARM推出了ARM DesignStart计划,开放了1000+IP的物理版图,2015年开源Cortex-M0 IP评估版本,2017年开源Cortex-M3 IP,2018年开源Cortex-A5 IP,提供了用户快速获取ARM IP的途径,通过提供的CPU和IP方案,用户可以更简单、更快速、更低风险的途径实现定制化SoC。

DesignStart计划可以让用户无需预付授权费用,就可以开始设计、制造基于Cortex-M0和Cortex-M3处理器的SoC,当产品成功量产出货之后再支付版税。

ARM Cortex-M0和Cortex-M3是全球使用最广泛的ARM处理器核,合计出货量超过200亿。

DesignStart包括多个版本,如面向个人的Eval和FPGA版本,面向企业用户的Physical和Pro版本,面向科研、教育方向的University版本,下面来具体看看都有什么区别。

1.DesignStart Eval版本

评估板IP核,任何人都可以通过官方网站免费申请获取Cortex-M0和Cortex-M3处理器及其子系统IP,内部为网表级Verilog代码,可读性较差。

2.DesignStart FPGA版本

FPGA版本,免费申请,针对FPGA进行了优化,可以以IP核的方式在开发环境中使用,目前只支持Xilinx和Gowin(高云)的开发环境,可以用于评估、教学和研究使用。

配合Keil、Jlink等ARM开发工具,在FPGA上实现ARM软核之后,就可以把FPGA当做一颗ARM内核的单片机来使用,和通用MCU使用方法无区别。

3.DesignStart Pro版本

专业版,面向希望开发ARM内核芯片的企业用户,在官方网站完成注册后,需要签署一份License授权文件,之后会获取到RTL级的Verilog代码,用户可以用来做定制化SoC,如功能增强,性能改进等,无需预付授权费,在产品成功流片上市之后才收取版税。

Cortex-M0和Cortex-M3处理器无需支付授权费。Cortex-A5处理器需要支付非常低的授权费,最多可提供3年的技术支持。

4.DesignStart Physical&University版本

物理实现IP版本可以加速芯片的物理版图设计实现,大学计划版本用于科研、教育方向的SoC设计。

Cortex-M3 Xilinx FPGA 软核下载

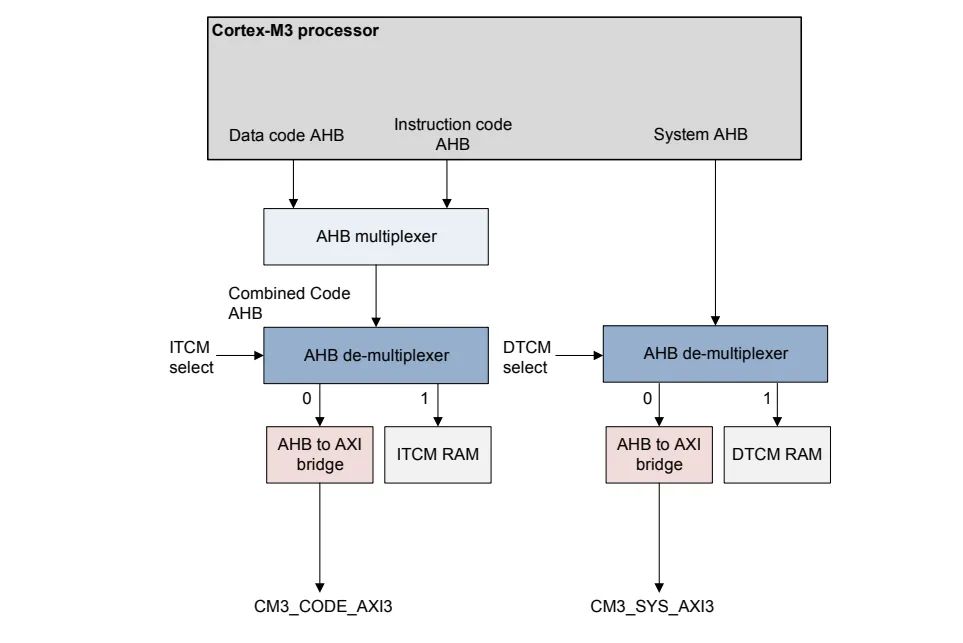

用户可以使用Xilinx Vivado环境,在FPGA上搭建一颗私人定制的ARM Cortex-M0或Cortex-M3内核的SoC,ARM DesignStart计划提供了处理器核,通过加入AXI总线,可以添加更多的AXI外设,如GPIO、UART、SPI、TIMER、INTC等。

转载:全栈芯片工程师

免责声明:文章内容来自互联网,本站不对其真实性负责,也不承担任何法律责任,如有侵权等情况,请与本站联系删除。

转载请注明出处:Cortex-M3 DesignStart FPGA-Xilinx-courtesy https://www.yhzz.com.cn/a/10040.html